Name\_\_\_\_\_

| 1) A LOW input to an inverter produces a HIGH output.                    | 1) |

|--------------------------------------------------------------------------|----|

| Answer:  True False                                                      |    |

| 2) The OR gate performs a function similar to series-connected switches. | 2) |

| Answer: True • False                                                     |    |

| 3) The output of an AND gate is HIGH only when all inputs are HIGH.      | 3) |

| Answer: • True False                                                     |    |

| 4) The output of an AND gate is LOW only when all inputs are LOW.        | 4) |

| Answer: True 💿 False                                                     |    |

| 5) When the inputs to a 3-input AND gate are 001, the output is HIGH.    | 5) |

| Answer: True 💿 False                                                     |    |

| 6) When the inputs to a 3-input OR gate are 001, the output is HIGH.     | 6) |

| Answer: True False                                                       |    |

| 7) The output of an OR gate is HIGH when at least one input is HIGH.     | 7) |

| Answer: True False                                                       |    |

| 8) The output of an OR gate is LOW when at least one input is LOW.       | 8) |

| Answer: True 🛛 False                                                     |    |

| 9) The output of a NAND gate is HIGH only when one or more inputs are HIGH.<br>Answer: True Selse                                  | 9)  |

|------------------------------------------------------------------------------------------------------------------------------------|-----|

| 10) The output of a NAND gate is LOW only when all inputs are HIGH.<br>Answer: True False                                          | 10) |

| <ul><li>11) The output of a NOR gate is LOW only when all inputs are HIGH.</li><li>Answer: True <ul><li>False</li></ul></li></ul>  | 11) |

| <ul><li>12) The output of a NOR gate is HIGH only when all inputs are HIGH.</li><li>Answer: True <ul><li>False</li></ul></li></ul> | 12) |

| 13) When the inputs to a 3-input NAND gate are 001, the output is HIGH.<br>Answer: True False                                      | 13) |

| 14) When the inputs to a 3-input NOR gate are 001, the output is LOW.<br>Answer: True False                                        | 14) |

| <ul><li>15) The output of a 2-input Exclusive-OR gate is H</li><li>Answer: True <ul><li>False</li></ul></li></ul> | IGH when the inputs are equal, or identical.   | 15)     |

|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------|---------|

| 16) The output of a 2-input Exclusive-NOR gate is<br>Answer: True False                                           | HIGH when the inputs are equal, or identical.  | 16)     |

| 17) A circle, or "bubble," on a distinctive-shape log<br>Answer: • True False                                     | ic symbol indicates a logic inversion.         | 17)     |

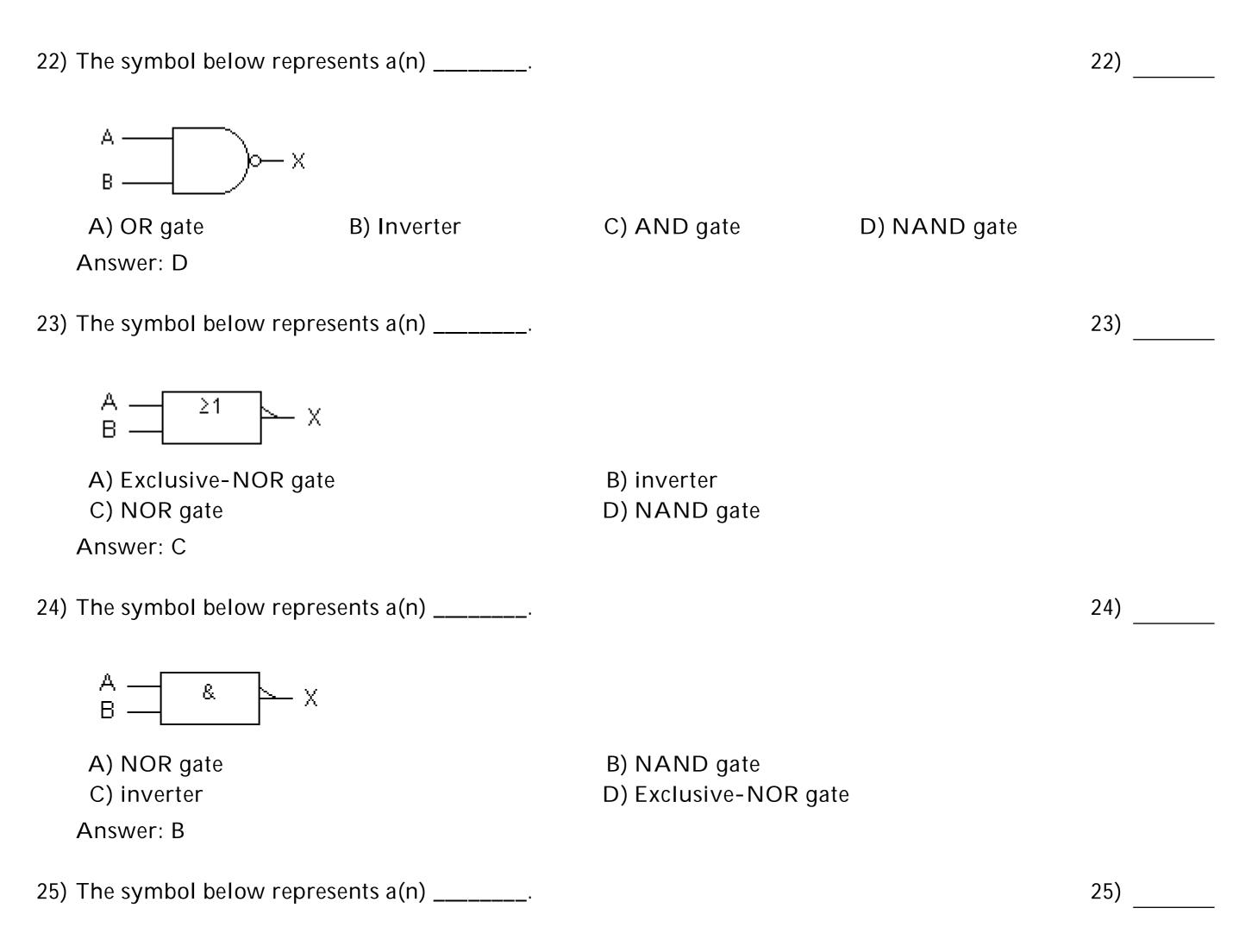

| MULTIPLE CHOICE. Choose the one alternative that b                                                                | est completes the statement or answers the que | estion. |

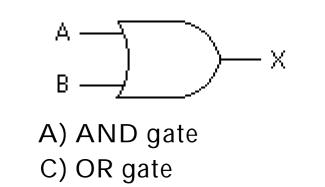

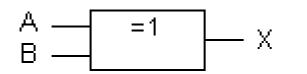

| 18) The symbol below represents a(n)                                                                              |                                                | 18)     |

| A                                                                                                                 |                                                |         |

| A) NAND gate                                                                                                      | B) AND gate                                    |         |

| C) OR gate                                                                                                        | D) none of the above                           |         |

| Answer: B                                                                                                         |                                                |         |

| 19) The symbol below represents a(n)                                                                              |                                                | 19)     |

| A & X<br>B X                                                                                                      |                                                |         |

| A) NAND gate                                                                                                      | B) AND gate                                    |         |

| C) OR gate                                                                                                        | D) none of the above                           |         |

| Answer: B                                                                                                         |                                                |         |

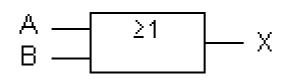

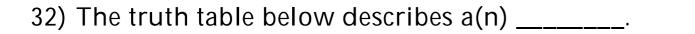

21)

Answer: C

21) The symbol below represents a(n) \_\_\_\_\_.

A) Inverter C) AND gate Answer: B

B) Inverter D) none of the above

B) OR gate D) none of the above

$A \rightarrow \overline{}$

A) AND gate B) NAND gate Answer: C

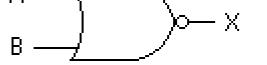

26) The symbol below represents a(n) \_\_\_\_\_.

A) OR gateC) NAND gateAnswer: B

B) Exclusive-OR gateD) AND gate

C) NOR gate

D) OR gate

26)

27) The symbol below represents a(n) \_\_\_\_\_.

A В

A) Exclusive-NOR gate B) Exclusive-OR gate C) NAND gate D) NOR gate Answer: A 28) The symbol below represents a(n) \_\_\_\_\_. 28) Α —— | ≫—× B) OR gate A) Inverter C) AND gate D) NAND gate Answer: A 29) The truth table below describes a(n) \_\_\_\_\_. 29) Х В 0 0 0 1 0 0 0 0 1 1 A) AND gate B) OR gate C) NOR gate D) NAND gate Answer: A

АВХ

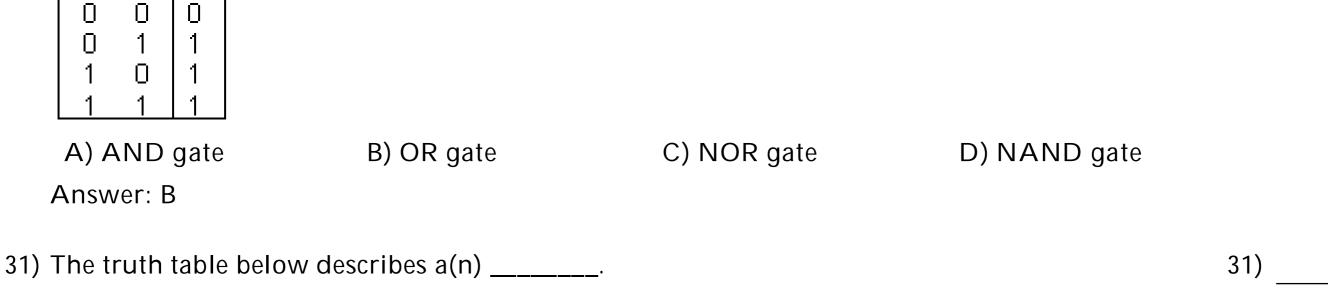

30) The truth table below describes a(n) \_\_\_\_\_.

30)

27)

| A | В | Х |

|---|---|---|

| 0 | 0 | 1 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

A) AND gate Answer: D B) OR gate

C) NOR gate

D) NAND gate

33) Which of the truth tables below describes the Exclusive-NOR gate?

| ABX       | ABX     | ABX     | ABX    |        |

|-----------|---------|---------|--------|--------|

| 0 0 1     | 0 0 1   |         |        |        |

|           | 0 1 1 1 | 0 1 1 1 |        |        |

| 1 0   0   | 1 0   1 | 1 0   1 |        |        |

|           |         |         |        |        |

| (A)       | (B)     | (C)     | (D)    |        |

| A) (A)    | B) (E   | 3)      | C) (C) | D) (D) |

| Answer: A |         |         |        |        |

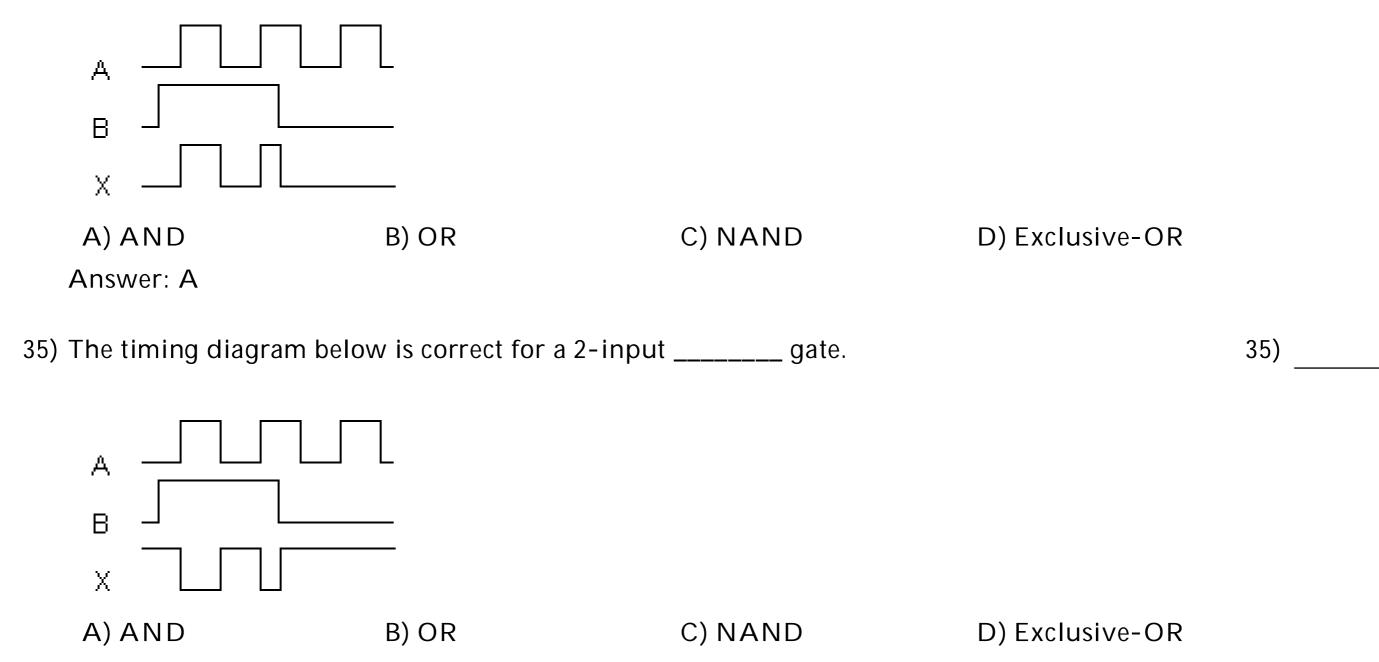

34) The timing diagram below is correct for a 2-input \_\_\_\_\_ gate.

33)

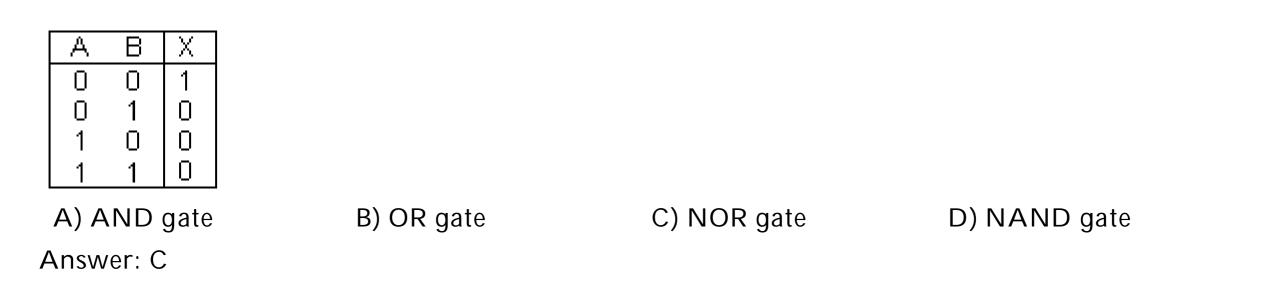

32)

Answer: C

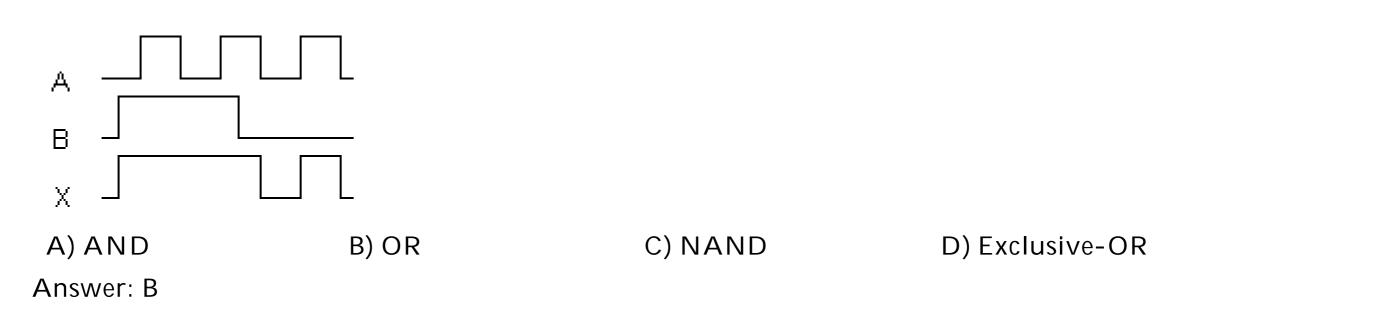

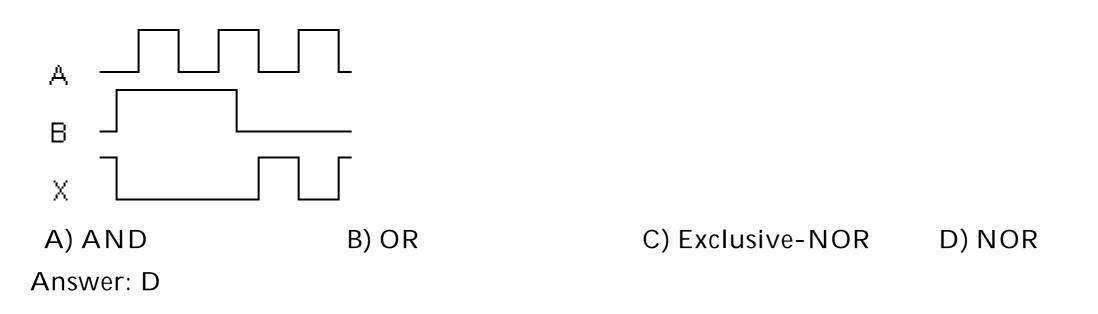

36) The timing diagram below is correct for a 2-input \_\_\_\_\_ gate.

36)

37)

37) The timing diagram below is correct for a 2-input \_\_\_\_\_ gate.

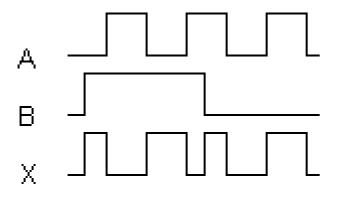

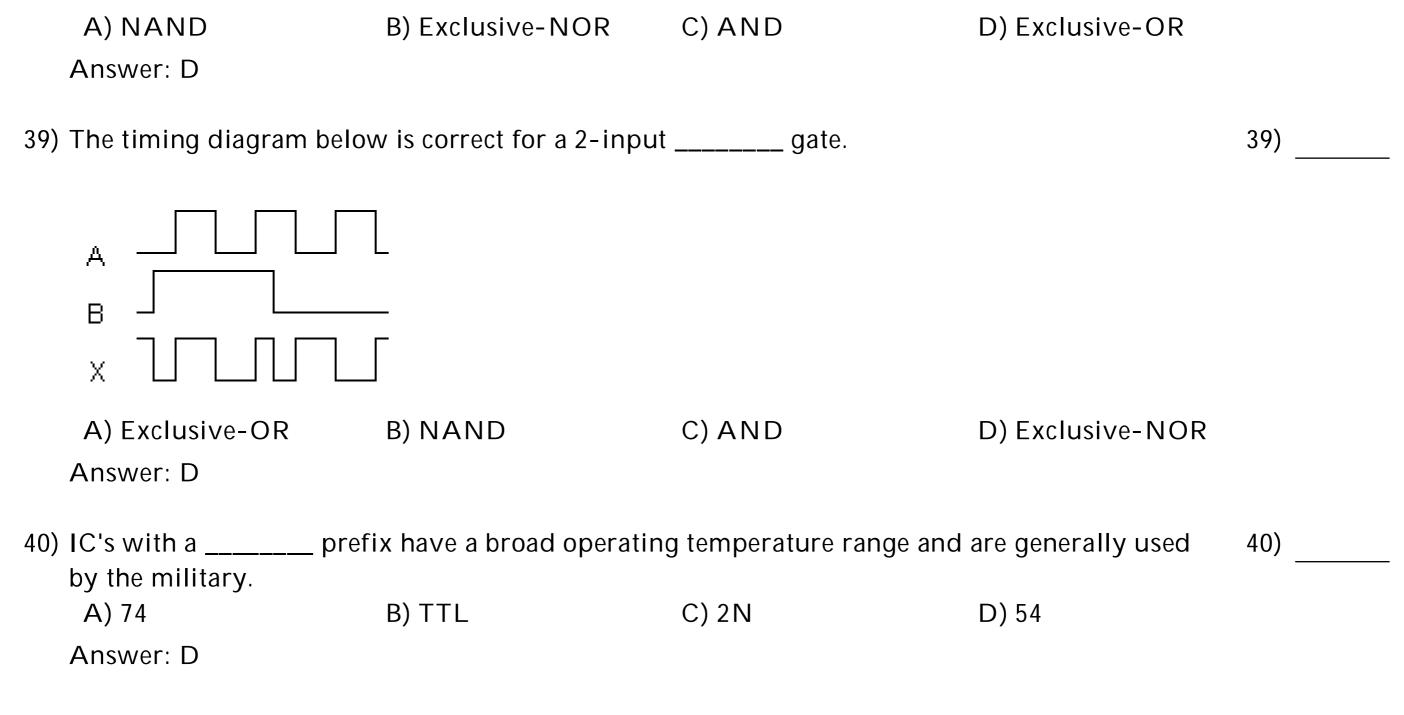

38) The timing diagram below is correct for a 2-input \_\_\_\_\_ gate. 38)

| 41) The<br>IC's.  | _ series of IC's are pin, function and                                | d voltage-level com  | patible with the 74 series     | 41) |

|-------------------|-----------------------------------------------------------------------|----------------------|--------------------------------|-----|

| A) ALS            | B) 2 N                                                                | С) НСТ               | D) CMOS                        |     |

| Answer: C         |                                                                       | ·                    | ·                              |     |

| •••               | draws 10mA when its output is HI<br>om a 12V supply with a 10% duty c |                      | -                              | 42) |

| <br>A) 228mW      | B) 360mW                                                              | C) 324mW             | D) 180mW                       |     |

| Answer: A         |                                                                       |                      |                                |     |

| 43) The fanout fo | or standard bipolar logic devices is                                  | ·                    |                                | 43) |

| A) 5              | B) 10                                                                 | C) 2                 | D) 1                           |     |

| Answer: B         |                                                                       |                      |                                |     |

| •                 | x inverter" refers to                                                 |                      |                                | 44) |

|                   | ters in a single package                                              | •                    | hich has six inputs            |     |

| Answer: A         | ter that has a history of failure                                     | D) a six-iliput s    | ymbolic logic device           |     |

| 45) Which type o  | of gate can be used to add two bits?                                  | 2                    |                                | 45) |

| A) XNAND          | B) NOR                                                                | C) NAND              | D) XOR                         |     |

| Answer: D         |                                                                       |                      |                                |     |

| 46) An AND gate   | e is checked for operation and the f                                  | following readings a | are taken on the gate: input   | 46) |

| -                 | put B = 4.5 V, input C = 0.4 V, outp                                  |                      | <b>°</b> °                     |     |

| A) Input C i      | 5                                                                     | , ,                  | s stuck high; the chip is bad. |     |

| · · ·             | out is too low: it should be 5 V.                                     | D) Nothing is w      | rong with the gate.            |     |

| Answer: B         |                                                                       |                      |                                |     |

| A) go LOW, beca<br>B) go HIGH, sin<br>C) react to the o | curs on the input to a bipo<br>ause there is no current in<br>ce full voltage appears ac<br>pen input as if it were a H<br>if only the good inputs ar | ross an open<br>IGH input             | t will  | 47) |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------|-----|

| Answer: C                                               |                                                                                                                                                       |                                       |         |     |

| A) go LOW, beca<br>B) go HIGH, sin<br>C) be treated as  | curs on the input of a CM<br>ause there is no current in<br>ce full voltage appears ac<br>if the open input were a H<br>able; it may go HIGH or L     | ross an open<br>HIGH                  |         | 48) |

| Answer: D                                               |                                                                                                                                                       |                                       |         |     |

| 49) What technology<br>A) TTL                           | allows a GAL to be repro<br>B) CMOS                                                                                                                   | grammed again and again?<br>C) E2CMOS | D) NMOS | 49) |

| <b>A</b>                                                |                                                                                                                                                       |                                       |         |     |

Answer: C

| A) OR arrays and<br>C) AND arrays o                                     | 5                                                                                                                        | B) OR arrays on<br>D) NOR arrays           | ly                    | 50) |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-----------------------|-----|

| Answer: A                                                               |                                                                                                                          |                                            |                       |     |

| 51) Which of the follow                                                 | wing is not a type of SPLD                                                                                               | )?                                         |                       | 51) |

| A) GAL                                                                  | B) RAM                                                                                                                   | C) PLA                                     | D) PROM               |     |

| Answer: B                                                               |                                                                                                                          |                                            |                       |     |

| 52) The difference bet                                                  | ween a PLA and a PAL is                                                                                                  |                                            |                       | 52) |

| ·                                                                       | nore possible product term                                                                                               |                                            |                       | ·   |

| only has a pro<br>C) the PAL has a<br>only has a pro                    | programmable OR plane<br>ogrammable AND plane<br>programmable OR plane<br>ogrammable AND plane<br>As are the same thing. |                                            |                       |     |

| Answer: B                                                               |                                                                                                                          |                                            |                       |     |

| 53) HDL stands for                                                      |                                                                                                                          |                                            |                       | 53) |

| A) hardwire desc                                                        | riptive logic                                                                                                            | B) hardware des                            | scription language    | ·   |

| C) hardwired dig                                                        | gital logic                                                                                                              | D) none of the al                          | bove                  |     |

|                                                                         |                                                                                                                          |                                            |                       |     |

| Answer: B                                                               |                                                                                                                          |                                            |                       |     |

|                                                                         | in that they inclu<br>eristics.                                                                                          | ide ways of describing                     | propagation times and | 54) |

| 54) HDLs differ from <u>.</u><br>other logic charact                    | •                                                                                                                        | ıde ways of describing<br>B) software digi |                       | 54) |

| 54) HDLs differ from <u></u><br>other logic charact<br>A) software prog | eristics.                                                                                                                |                                            | tal logic             | 54) |

| A) source | B) hardware                     | C) entity           | D) architecture | 55) |

|-----------|---------------------------------|---------------------|-----------------|-----|

| Answer: C |                                 |                     |                 |     |

| 56) The   | _ in a VHDL program describes i | ts logic operation. |                 | 56) |

| A) source | B) architecture                 | C) entity           | D) hardware     |     |

| Answer: B |                                 |                     |                 |     |

A) VHDL B) HDL C) fixed-function D) microcontroller Answer: C